如图,这样就可以调用系统默认浏览器打开网页。

Certified LabVIEW Developer 认证小结

LabVIEW中级认证考试的主要目的就是考察受试者的LabVIEW编程水平,程序风格,文档注释三个方面.详细可以查看下面的文档

ftp://ftp.ni.com/pub/devzone/tut/cld_exam_preparation_guide.pdf

下面这个链接已经列举了一些注意事项,我再补充几条:

http://cygnus-wei.spaces.live.com/blog/cns!CD5F4D351CB23EC!1406.entry

1. 善于利用LabVIEW自带的模板和VI,例如定时迅捷VI,读写电子表格文件VI,状态机模板,子VI模板几个都要熟练掌握.

2. 最好使用LabVIEW英文版开发环境.这样无论是模板还是控件名字都是默认英文,可以减小工作量.

3. 不要忘记在状态机模板里加上错误处理.

4. 写完程序一定要留调试和注释的时间.

5. 尽量将状态机Case结构里的代码封装为子VI.

6. 能用TypeDefine控件的尽量都用TypeDefine控件,方便程序维护.

7. 不需要用户交互的前面板控件最好隐藏掉.

细节:

1. 框图和前面板大小:根据考试要求最好限定为1024x768,要扩展尽量水平扩展.现在显示器以宽屏居多,方便观察整个程序.

2. LabVIEW配置,如果你到手的机器配置修改太多,例如字体等要改回来很麻烦.最简单的办法就是删除LabVIEW的INI文件.然后在工具->属性里取消前面板控件:显示为图标.

3. 状态机里面的等待函数一定要修改,设置为1是个不错的选择.

4. 使用Ctrl+鼠标拖拽扩展程序框图时一定要慎重,避免程序连线错位.

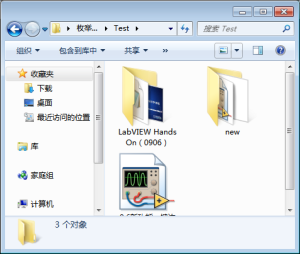

LabVIEW 2009递归研究

Part I : Handson

各位安装LabVIEW2009的同学请跟我做以下动作:

1:打开LabVIEW 2009.

[](https://f2gz7g.bay.livefilestore.com/y1mJf781TsQY2lMDPJPSS-Ciy9j5BqCKwwYq4up4HegzWdSPRRoK9XmPUSm0MhcjjsGdO3yBFl5o2ZUoHcAEFlDD9Idvou3kEx52H_zGgNN4Qq5OZzivi1JsoCTqmPU_J_g-6lkWGxiRub0O8NdLW8Kxw/image2 7AFEC386.png)

2:Ctrl+N

[](https://f2gz7g.bay.livefilestore.com/y1mqUA4E2HIjdW9Gb3BZtx2IS9OvqufNm9ay5c3yoX7YyZtiExwtvNyKY6zO4IzSS5_hYD1H1mT82bnVU8GrzxlS_AzTvrzEsxkIBloXGJEeXVT03GQDPTy5-7VXeuYh0kU6fKN5Cf7WXnw8gIPYYITWQ/image8 2D5308B1.png)

3:Ctrl+I,按下图配置

4:Ctrl+E,选择程序框图,将图标拖到程序框图

5:Ctrl+R,然后稍等5分钟:

恭喜你编写了第一个递归VI并且让他挂掉了。

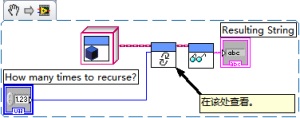

** Part II : Basic I**

好,我们来玩点实在的,先看看LabVIEW 的例程:

在LabVIEW以前的版本只有类才能使用递归,不过现在已经比较成熟,普通的VI也可以递归了。

注意事项正如图中注释,我就不多废话。

Part III : Basic I

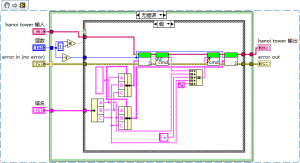

为了更详细的演示递归,我们请出教科书里的经典例程汉诺塔。

首先附赠一个汉诺塔小游戏:

附赠小游戏汉诺塔下载:

#include <stdio.h> void hano(int n,char a,char b,char c) { if(n==1) printf("t将%d个盘片从%c移动到%cn",n,a,c); else { hano(n-1,a,c,b); printf("t将第%d个盘片从%c移动到%cn",n,a,c); hano(n-1,b,a,c); } } main() { int n; printf("输入将要移动多少个盘子n:"); scanf("%d",&n); printf("递归结果:n"); hano(n,'x','y','z'); }

然后我们来看看LabVIEW里面如何实现这个算法:

主程序调用算法,然后演示步骤。

递归调用算法。

当然不要忘记设置退出递归的条件。

源代码下载

Part IV : Advance I

到底递归有什么用呢?我们来看一个实用一点的工具:VI图标提取器

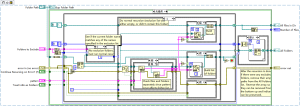

主程序:

![]()

递归代码

![]()

源目录

输出目录

Part V : Advance II

另外程序里附赠了一个利用LabVIEW自带的枚举函数写的同功能VI,大家可以看看,这个是可以枚举llb的。

最后总结一下递归要注意的事项:

1:真的有必要用递归么?

2:你的程序能否正常退出递归?

3:递归的过程是无法直接调试的,有没有好的办法保证VI按照我们的预期执行?

如果这三个问题都能保证,恭喜你,你可以使用递归来提高你程序的效率了。

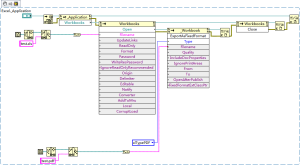

[代码分享]将Excel报表转换为PDF

有的时候我们往往不希望操作人员能修改生成的报表,转换为PDF就是一种不错的解决办法.

http://decibel.ni.com/content/docs/DOC-4552

这就是一种不错的方案,不过需要安装一个软件才行。

其实Office2007SP2自带了转换为PDF的功能,调用的代码如下:

拖到LabVIEW2009里面可以转换为代码。

Msdn的例程:

NI 驱动下载一览表

第一项 NI Device Driver CD,现在可能叫Device Driver DVD更好一些。

目前最新版2009年8月驱动下载地址:

ftp://ftp.ni.com/support/drivercd/2009.08/dcd-aug09-1.exe

ftp://ftp.ni.com/support/drivercd/2009.08/dcd-aug09-2a.exe

ftp://ftp.ni.com/support/drivercd/2009.08/dcd-aug09-2b.exe

三个包下载完毕以后依次解压即可。

通用下载地址(包含所有版本):

ftp://ftp.ni.com/support/drivercd/

第二项 高精度温度记录仪驱动,NI 435x系列驱动。

目前最新版 NI 435x 2.5.2下载地址:

ftp://ftp.ni.com/support/NI-435x/2.5.2/NI435X252.zip

通用下载地址:

ftp://ftp.ni.com/support/NI-435x/

第三项 NI同步板卡驱动,NI 665x系列板卡驱动。

目前最新版 NI Sync 3.1下载地址:

ftp://ftp.ni.com/support/softlib/Timing_Sync/3.1/NISync310.zip

介绍页面:

http://joule.ni.com/nidu/cds/view/p/id/1367/lang/zhs

Readme:

http://ftp.ni.com/support/softlib/Timing_Sync/3.1/readme.htm

所有版本下载地址:

ftp://ftp.ni.com/support/softlib/Timing_Sync/

第四项 NI低噪音放大器驱动,对应NI 5690板卡。

最新1.0.6下载地址:

ftp://ftp.ni.com/support/softlib/RF/NI-5690/1.0.6/NI5690106.ZIP

所有版本下载地址:

ftp://ftp.ni.com/support/softlib/RF/NI-5690/

第五项 NI中频收发器驱动,对应NI 564x系列板卡。

最新1.3下载地址

http://ftp.ni.com/support/softlib/RF/NI-5640R/1.3/NI5640R130.zip

所有版本下载地址:

ftp://ftp.ni.com/support/softlib/RF/NI-5640R/

第六项 PXI控制器驱动:

Trigger Bus,Watchdog driver(8130 for Vista/Server2008/7/Server2008R2 64bit/32bit)

[ftp://ftp.ni.com/support/pxi/pxie-8130/PXIe-8130%20Peripherals%20(VISTA).zip](ftp://ftp.ni.com/support/pxi/pxie-8130/PXIe-8130 Peripherals (VISTA).zip)

其他:

第七项 流盘驱动:

http://digital.ni.com/public.nsf/allkb/5D08C51AF3C748BD86257560000F7E44

8264

8263

http://digital.natinst.com/public.nsf/$CXIV/ATTACH-AEEE-7EUTDF/$FILE/HDD-8263_Version_v2.2_XP.zip

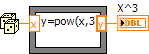

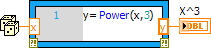

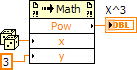

WE DO THE 3RD POWER OF X RIGHT(2)+LabVIEW Unit Test Framework Toolkit 1.0试用

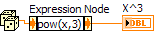

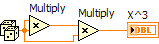

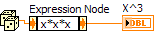

上回我们说到茴香豆有四种写法X的立方已经有四种办法可以搞定,下面我们来看看更多得办法~

使用公式节点也可以

M脚本也可以

微软的.NET也可以

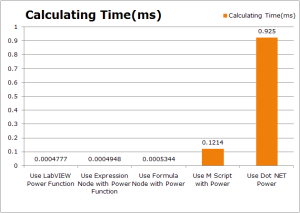

如果我们都使用同样的算法,到底这几种接口有没有不同,那种效率更高呢?

我们还是用事实说话:

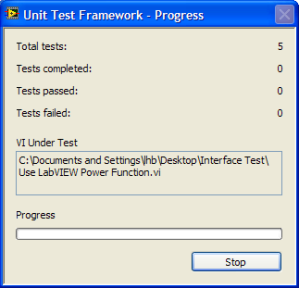

首先有请 LabVIEW Unit Test Framework Toolkit 1.0 for LabVIEW 8.6.1

安装好以后我们就可以对LabVIEW VI进行自定义的测试了

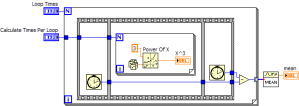

我们来回顾一下程序代码这里我把循环次数都变为控件

然后新建一个测试

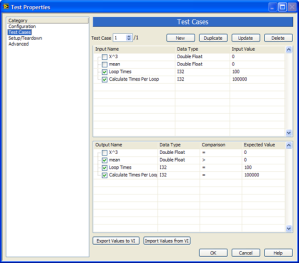

配置输入和输出参数

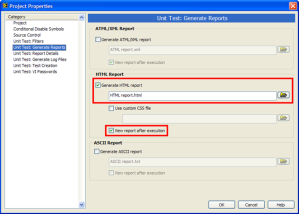

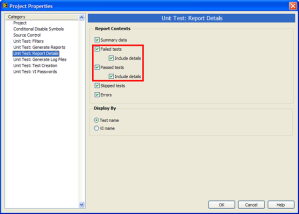

别忘了在工程里面配置一下报表

点击运行测试就可以让LabVIEW替我们干活了

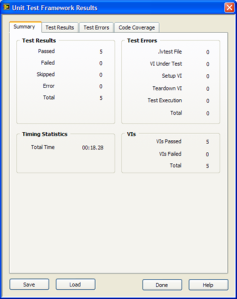

大功告成~

我们来总结一下~

| Use LabVIEW Power Function | Use Expression Node with Power Function | Use Formula Node with Power | Use M Script with Power | Use Dot NET Power | |

| Calculating Time(ms) | 0.0004777 | 0.0004948 | 0.0005344 | 0.1214 | 0.925 |

从表格和下图可以看出**LabVIEW的原生节点和框图效率都还不错,使用外部接口和脚本时效率较低。**

另付LabVIEW Unit Test Framework Toolkit的测试报告:

The 3rd Power of X

Time: 2009-3-27 14:54:04

Operator: lhb

Operating System: Windows NT 5.1

LabVIEW Version: 8.6.1 (en)

Test Summary

0 Test Errors

0 Tests Failed

0 Tests Skipped

5 Tests Passed

Time elapsed: 00:00:36

Test Results

Failed

None.

Passed

| Test Name | Test Location | VI Name | Test Cases | Duration [s] | Code Coverage [%] | Requirements |

|---|---|---|---|---|---|---|

| [Use LabVIEW Power Function.lvtest](#Link0) | My Computer/LabVIEW Block Diagram | Use LabVIEW Power Function.vi | 1 | 5.77 | 100.0 | |

| [Use Expression Node with Power Function.lvtest](#Link1) | My Computer/Expression Node | Use Expression Node with Power Function.vi | 1 | 5.91 | 100.0 | |

| [Use Formula Node with Power.lvtest](#Link2) | My Computer/Fomula Node | Use Formula Node with Power.vi | 1 | 6.20 | 100.0 | |

| [Use M Script with Power.lvtest](#Link3) | My Computer/M SCRIPT | Use M Script with Power.vi | 1 | 2.03 | 100.0 | |

| [Use Dot NET Power.lvtest](#Link4) | My Computer/Dot NET | Use Dot NET Power.vi | 1 | 1.77 | 100.0 |

Test Details

1. My Computer

1.1. LabVIEW Block Diagram

1.1.1. Use LabVIEW Power Function.lvtest

| VI Under Test: | C:Documents and SettingslhbDesktopInterface TestUse LabVIEW Power Function.vi |

| Result: | Passed |

| VI Timestamp: | 2009-3-27 11:59:53 |

| VI Revision: | 10 |

| Test Started: | 2009-3-27 14:53:27 |

| Test Duration: | 00:00:06 |

| Code Coverage: | 100.0 % |

| Setup VI: | |

| Teardown VI: |

- Test Case 1: Passed**1.2. Expression Node

1.2.1. Use Expression Node with Power Function.lvtest

**VI Under Test: C:Documents and SettingslhbDesktopInterface TestUse Expression Node with Power Function.vi Result: Passed VI Timestamp: 2009-3-27 11:59:53 VI Revision: 6 Test Started: 2009-3-27 14:53:33 Test Duration: 00:00:06 Code Coverage: 100.0 % Setup VI: Teardown VI:

1.3. Fomula Node

1.3.1. Use Formula Node with Power.lvtest

| VI Under Test: | C:Documents and SettingslhbDesktopInterface TestUse Formula Node with Power.vi |

| Result: | Passed |

| VI Timestamp: | 2009-3-27 13:56:38 |

| VI Revision: | 12 |

| Test Started: | 2009-3-27 14:53:40 |

| Test Duration: | 00:00:06 |

| Code Coverage: | 100.0 % |

| Setup VI: | |

| Teardown VI: |

1.4. M SCRIPT

1.4.1. Use M Script with Power.lvtest

| VI Under Test: | C:Documents and SettingslhbDesktopInterface TestUse M Script with Power.vi |

| Result: | Passed |

| VI Timestamp: | 2009-3-27 14:19:42 |

| VI Revision: | 11 |

| Test Started: | 2009-3-27 14:53:58 |

| Test Duration: | 00:00:02 |

| Code Coverage: | 100.0 % |

| Setup VI: | |

| Teardown VI: |

1.5. Dot NET

1.5.1. Use Dot NET Power.lvtest

| VI Under Test: | C:Documents and SettingslhbDesktopInterface TestUse Dot NET Power.vi |

| Result: | Passed |

| VI Timestamp: | 2009-3-27 11:59:53 |

| VI Revision: | 12 |

| Test Started: | 2009-3-27 14:54:01 |

| Test Duration: | 00:00:02 |

| Code Coverage: | 100.0 % |

| Setup VI: | |

| Teardown VI: |

WE DO The 3rd Power of X RIGHT(1)

我们常常有这样一个错觉,在LabVIEW里面使用文本性的代码往往执行效率不如原生的框图高,究竟是不是这样呢?

我们可以看看下面这个例子,如何才能最快的在LabVIEW里计算出X的三次方:

首先我们看看几种计算立方常用的办法(对啦,茴香豆有几种写法啊?)

1:LabVIEW math选版的幂函数VI

2:表达式节点的power函数

3:用乘法VI连乘(简单好用就是硬道理)

4:对啦!连乘而已,表达式节点一样能搞定

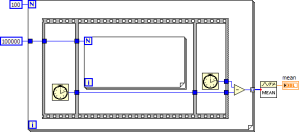

为了测试出到底每种花了多少时间,我们首先记录下算法计算100,000次所花的时间,然后为了消除单次计数的误差,我们循环100次然后平均,最后得出每种算法花费的时间。

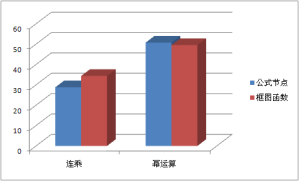

下面是程序运行的结果,为了保证不互相影响,所有VI都提前打开并运行一次,以确保内存都已分配,结果如下图

| 连乘 | 幂运算 | |

| 公式节点 | 28.84 | 50.8 |

| 框图函数 | 34.4 | 49.55 |

可以看出来,LabVIEW 执行文本代码和框图代码效率基本相同,而且改进算法的影响要远远大于代码的表现形式。

附程序执行截屏一张,大图杀猫!

LabVIEW 图标编辑器相关技巧两则

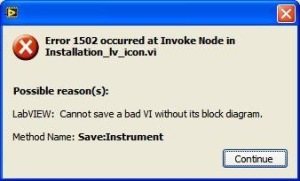

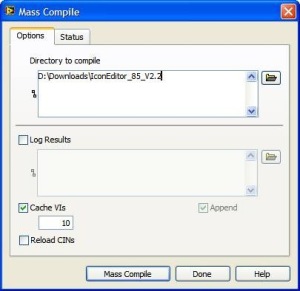

1. 在LabVIEW 8.6下安装图标编辑器报错的解决

下载的安装包直接运行会提示以下错误

重启后打开图标编辑器闪过新界面后还是原来的编辑器。

以下是解决方案:MASScompile整个目录

再次安装即可正常使用

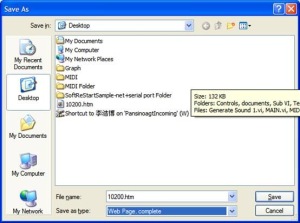

2. 批量获取新图标

1)浏览到合适网页,选择另存全部网页.

这时候我们就有了大量的新图标,不过透明的部分在不支持alpha通道的软件(LabVIEW、画图等)里会显示黑块。

2)此时合该祭出PS

我们以PS化之

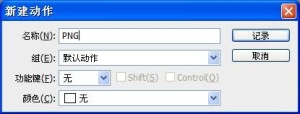

3)打开一个图标,打开动作面板,我们新建一个动作

然后另存为PNG

[![clip_image032[1] clip_image032[1]](http://lhb5883.files.wordpress.com/2009/02/clip_image0325b15d5b25d.jpg?w=224) ](http://lhb5883.files.wordpress.com/2009/02/clip_image0325b15d5b25d.jpg)

](http://lhb5883.files.wordpress.com/2009/02/clip_image0325b15d5b25d.jpg)

关闭GIF文件后结束动作录制。

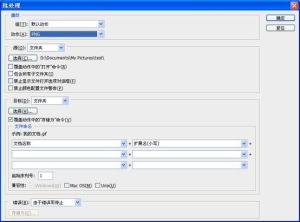

使用文件菜单下批处理,配置好输入输出目录静待PS发威。

4)然后我们打开PNG,再建一个转换背景的动作

首先更改颜色到RGB模式

然后添加背景

最后保存关闭,结束录制

再批处理一次

5)最后复制到相应路径下即可使用

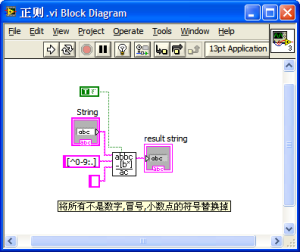

LabVIEW 正则表达式应用

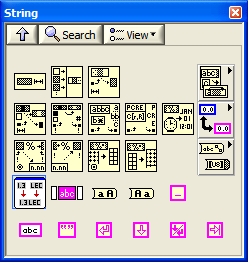

在传统的文本式编程里,最常用的字符串处理方法就是正则表达式。在LabVIEW里面,虽然也提供了大量的文本处理函数包括查找替换等等,供我们处理字符串。

不过LabVIEW里面也提供了正则表达式这一强大的工具:

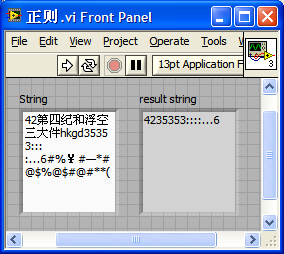

下面我们看看这个例子,将输入字符串的数字、冒号、小数点保留,其他字符去掉。

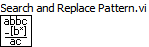

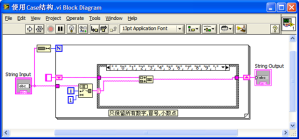

使用Case结构和字符串函数:

然后可以看看用正则表达式实现:

可以看到正则表达式是一个非常强大的工具。推荐两篇文档可以看看

正则表达式30分钟入门教程

[http://unibetter.com/deerchao/zhengzhe-biaodashi-jiaocheng-se.htm](http://unibetter.com/deerchao/zhengzhe-biaodashi-jiaocheng-se.htm "http://unibetter.com/deerchao/zhengzhe-biaodashi-jiaocheng-se.htm")

Introduction to Regular Expressions(MSDN)

[http://msdn.microsoft.com/en-us/library/28hw3sce.aspx](http://msdn.microsoft.com/en-us/library/28hw3sce.aspx "http://msdn.microsoft.com/en-us/library/28hw3sce.aspx")

如何加速FPGA开发?

NI LabVIEW FPGA模块提供了一个非常方便的接口供我们以LabVIEW图形化的方式开发FPGA程序,不过也有令人困扰的问题就是LabVIEW FPGA代码编译的速度较慢,如果机器的配置不够高就是一件折磨人的事情。

所以今天给大家介绍几个小技巧:

1. IPnet

对于LabVIEW开发者,最常用的就是范例查找器这个工具,俗话说得好:“有范例,无问题。”

对于FPGA,还有一个非常好的工具:

LabVIEW FPGA IPNET

[http://zone.ni.com/devzone/cda/tut/p/id/6870](http://zone.ni.com/devzone/cda/tut/p/id/6870 "http://zone.ni.com/devzone/cda/tut/p/id/6870") >

LabVIEW FPGA IPNET是您浏览、领会和下载LabVIEW FPGA函数或IP(知识产权)的一站式资源中心。下表是从LabVIEW FPGA函数调色板、NI内部开发人员和LabVIEW FPGA社区收集的FPGA IP与范例的集合。您应当使用这一资源中心,以获取您的应用所需的IP、下载范例以帮助掌握编程技术和深入探究LabVIEW FPGA平台所提供的IP。除了探究这里所提供的资源外,您也可以通过点击下面的链接,为LabVIEW社区共享您的LabVIEW FPGA IP或者提交您对现有IP的更新。

IP是知识产权的缩写,这里就是指NI FPGA的算法。

2.LabVIEW验证

当我们自己写好一个算法或者我们找到了别人写好的IP以后,为了减少编译后在返工的情况,我们可以在LabVIEW里面验证一下算法是否有逻辑问题。

A:在My Computer新建一个VI把FPGA算法复制进去,然后在My Computer下调试。

B:在建好的VI下修改程序运行的位置。

[](https://aftv2q.bay.livefilestore.com/y1m16CiQX4LAsE9oz0_nT9oAPGaxircpCKDunowiDEkwRpRA8a_dtd1ahoztEJzH2fLqq5VONClJxbx-wJJMajnGrCfGRRqIDe4wDsKqggbfhOSFMOWLVfPRm--pW4RPUSotvSRaw6JaIs/image[3].png)

3.设置Compile Server:

LabVIEW FPGA编译过程是比较长的,并且速度和计算机配置有关,我们可以在一台机器上开发,另一台机器上编译,这样可以节约时间。

首先在服务器端打开compileServer,并确保防火墙开放96端口或者关闭防火墙,

[](http://lhb5883.files.wordpress.com/2009/02/image5b65d.png) [](http://lhb5883.files.wordpress.com/2009/02/image5b175d.png)

然后在客户端LabVIEW工具菜单下打开FPGA Module Option,点击Configure按钮,在Machine下输入服务器IP地址,点击OK保存,这样在编译FPGA时就会调用服务器进行。

[](http://lhb5883.files.wordpress.com/2009/02/image5b125d.png) [](http://lhb5883.files.wordpress.com/2009/02/image5b165d.png)

附 FPGA代码的编译过程:

首先将LabVIEW 程序框图转换为临时文件,然后传输到编译服务器生成和优化VHDL代码,最后编译为bitfile供下载到FPGA执行。

其中最耗时就是LabVIEW生成VHDL这一步,因为从图形化代码到逻辑电路关系的翻译需要大量的运算,除此之外还要为FPGA芯片优化,提高执行效率,这样就导致要花费较多的时间。